Flip Flop

Flip-flop adalah rangkaian utama dalam logika

sekuensial. Counter, register serta rangkaian sekuensial lain disusun dengan

menggunakan flip-flop sebagai komponen utama. Flip-flop adalah rangkaian yang

mempunyai fungsi pengingat (memory). Artinya rangkaian ini mampu melakukan

proses penyimpanan data sesuai dengan kombinas imasukan yang diberikan

kepadanya. Data yang tersimpan itu dapat dikeluarkan sesuai dengan kombinasi

masukan yang diberikan.

Ada beberapa macam flip-flop yang akan dibahas, yaitu

flip-flop R-S, flip-flop J-K, dan flip-flop D. Sebagai tambahan akan dibahas

pula masalah pemicuan yang akan mengaktifkan kerja flip-flop.

Sedangkan fungsi

rangkaian flip-flop yang utama adalah sebagai memori (menyimpan informasi) 1

bit atau suatu sel penyimpan 1 bit. Selain itu flip-flop juga dapat digunakan

pada Rangkaian Shift Register, rangkaian Counter dan lain sebagainya.

Macam - macam Flip-Flop:

1. RS Flip-Flop

2. D Flip-Flop

3. T Flip-Flop

4. CRS Flip-Flop

5. J-K Flip-Flop

1. RS

Flip-Flop

RS Flip-Flop yaitu

rangkaian Flip-Flop yang mempunyai 2 jalan keluar Q dan Q (atasnya digaris).

Simbol-simbol yang ada pada jalan keluar selalu berlawanan satu dengan yang

lain. RS-FF adalah flip-flop dasar yang memiliki dua masukan yaitu R (Reset)

dan S (Set). Bila S diberi logika 1 dan R diberi logika 0, maka output Q akan

berada pada logika 0 dan Q not pada logika 1. Bila R diberi logika 1 dan S

diberi logika 0 maka keadaan output akan berubah menjadi Q berada pada logik 1

dan Q not pada logika 0.

Sifat paling penting dari Flip-Flop adalah bahwa

sistem ini dapat menempati salah satu dari dua keadaan stabil yaitu stabil I

diperoleh saat Q =1 dan Q not = 0, stabil ke II diperoleh saat Q=0 dan Q not =

1

Dengan

adanya gerbang AND tersebut, R dan S akan berkeadaan 0 bila pulsa penabuh CP

(Clock Pulse) berkeadaan 1 dan flip-flop tidak akan berubah keadaan. Tanpa

pulsa penabuh, artinya CP=0, maka apapun perubahan yang terjadi pada masukan R

dan S tidak akan mengubah keadaan flip-flop. Rangkaian flip-flop itu akan

merasakan keadaan R dan S hanya bila CP= 1. Tabel kebenaran flip-flop RS

ditabuh ini untuk CP= 1 tepat sama dengan tabel kebenaran rangkaian dasar

flip-flop RS.

Perlu

dicatat bahwa dalam bentuk rangkaian terpadu banyak flip-flop RS yang diberikan

kelengkapan untuk menyetel dan mereset flip-flop melalui masukan terpisah yang

diberi nama masukan PRESET dan CLEAR, misalnya IC tipe SN74279 atau SN74LS279.

2.

Flip-flop D

Nama

flip-flop ini berasal dari Delay. Flip-flop ini mempunyai hanya satu masukan,

yaitu D. Jenis flip-flop ini sangat banyak dipakai sebagai sel memori dalam

komputer. Pada umumnya flip-flop ini dilengkapi masukan penabuh seperti ditunjukkan

pada Gambar 6.10. Keluaran flip-flop D akan mengikuti apapun keadaan D pada

saat penabuh aktif, yaitu: Q+ = D.

Perubahan

itu terjadi hanya apabila sinyal penabuh dibuat berlogika 1 (CP=1) dan tentunya

akan terjadi sesudah selang waktu tertentu, yaitu selama tundaan waktu pada

flip-flop itu. Bila masukan D berubah selagi CP = 0, maka Q tidak akan

terpengaruh. Keadaan Q selama CP= 0 adalah keadaan masukan D tepat sebelum CP

berubah menjadi 0. Dikatakan keadaan keluaran Q dipalang (latched) pada

keadaan D saat perubahan CP dari aktif ke tak-aktif. Dapat dilihat bahwa

sebenarnya flip-flop D berfungsi seperti apa yang dilakukan oleh flip-flop JK

bila masukan masukan K dihubungkan dengan komplemen masukkan J.

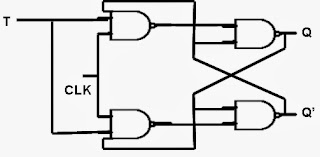

3. Flip

Flop T

Nama

flip-flop T diambil dari sifatnya yang selalu berubah keadaan setiap ada

sinyal pemicu (trigger) pada masukannya. Input T merupakan

satu-satunya masukan yang ada pada flip-flop jenis ini sedangkan keluarannya

tetap dua, seperti semua flip-flop pada umumnya. Kalau keadaan keluaran

flip-flop 0, maka setelah adanya sinyal pemicu keadaan-berikut menjadi 1 dan

bila keadaannya 1, maka setelah adanya pemicuan keadaannya berubah menjadi 0.

Karena sifat ini sering juga flip-flop ini disebut sebagai flip-flop toggle

(berasal dari skalar toggle/pasak).

4. Flip

Flop CRS

CRS Flip-flop adalah clocked RS-FF yang dilengkapi dengan  sebuah

terminal pulsa clock. Pulsa clock ini berfungsi  mengatur keadaan Set dan

Reset. Bila pulsa clock berlogik 0, maka perubahan logik pada input R dan

S tidak akan  mengakibatkan perubahan pada output Q dan Qnot. Akan

tetapi apabila pulsa clock berlogik 1, maka perubahan pada input R

dan S dapat mengakibatkan perubahan pada output QÂ dan Q not.

5. Flip

Flop JK

Flip-flop JK yang diberi nama

berdasarkan nama masukannya, yaitu J dan K. Flip-flop ini mengatasi kelemahan

flip-flop RS, yang tidak mengizinkan pemberian masukan R=S= 1, dengan

meng-AND-kan masukan dari luar dengan keluaran seperti dilakukan pada flip-flop

T. Dengan susunan ini, maka masukan J dan K berfungsi tepat sama dengan

masukan S dan R pada flip-flop RS, kecuali untuk J=K=1. Kalau pada flip-flop RS

masukan R=S=1 terlarang, maka pada flip-flop JK, masukan J=K=1 akan membuat

flip-flop JK

berfungsi seperti flip-flop T.

Read full post »